- 2008.12.30 Pipeline과 RISC 2 / Double-J

- 2008.02.12 [Study] PS/2 port (keyboard) 3 / Double-J

Double-J's World » Search » Results » Articles

Embedded와 관련된 글 2개

Pipeline과 RISC

Double-J | 2008. 12. 30. 23:55

RISC구조의 CPU가 좀더 Pipeline적용에 수월하다는 것이죠.

(CISC에도 Pipeline이 적용되어있습니다. 80486부터 당당하게요^^)

그럼 RISC는 어떻길래 Pipeline에 적용이 더 수월하다는 것일까요?

일단 Pipeline이 적용되지 않은상태에서 데이터 처리과정을 보겠습니다..

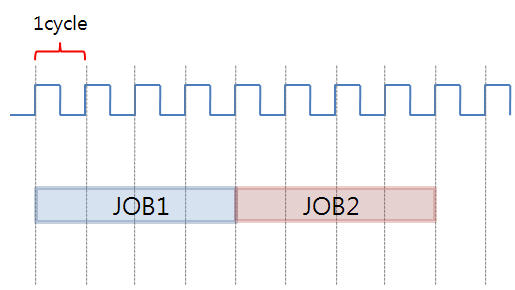

위의 그림은 어떤 두가지의 다른 데이터처리(job1, job2)가 CPU의 클럭에 맞춰 처리되는 상황을 표현한것입니다.

Pipeline이 적용되지 않는다면 다음과 같이 CPU에 입력된 순서대로 데이터 처리를 할 것입니다.

문제는 없어보입니다. 다만 JOB1이 모두 처리된후 JOB2가 모두 처리되기까지의 시간이

너무 길다는것이죠(4cycle이나..)

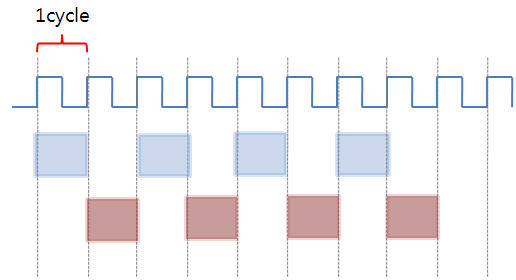

Pipeline이 적용된 상태에서의 데이터 처리과정은 다음과 같습니다.

파란색 부분 4조각을 합쳤을때 JOB1 이고 빨간색 부분 4조각을 합쳤을때가 JOB2와 같습니다.

마지막 끝나는 시간을 보면 총 8cycle로 이게 적용되나 적용되지 않으나 큰차이가 없어보입니다.

하지만 JOB1이 끝나자마자 1cycle후 JOB2가 끝났다는게 다른점이죠

물론 처음 한번 되기까지가 여러 cycle이 걸리지만 일단 첫번째 입력된 데이터 처리가 끝나기만하면

그다음부터는 1cycle씩 마다 데이터처리(JOB)이 처리되기 시작합니다.

마치 공장의 컨베이어벨트 처럼 자동차 한대를 만드는데 여러작업이 있는데 컨베이어벨트가 이동하면서

맡은 작업이 이루어지고 공장이 가동된지 가장 처음 나오는 자동차가 만들어지는 시간은 오래 걸리지만

일단 한번 처음 만들어진 자동차가 나오기 시작하면 그다음부터는 계속 생산되는것 처럼 상상해보시면

됩니다.

제가 그림 그리는것의 귀차니즘(?)의 압박이 있어 데이터 처리과정을 두개밖에 표현을 안했지만

저 데이터처리과정이 수천개 수만개가 되면 파이프라인의 효과는 체감상 엄청난 것입니다.

물론 위는 제가 가상으로 정한 시나리오입니다. 1cycle마다 된다는 보장도 없고 여러cycle이 걸릴수도 있고

일련의 데이터처리 사이에 다른 작업이 들어있을수도있지만 최대한 단순화시켜서 표현해본것 입니다.

그런데 위의 Pipeline동작은 데이터 처리과정에 입력(input)되는 데이터의 크기가 일정해야지 Pipeline의 효과를

극대화할 수 있습니다. 입력되는 데이터들마다 크기가 제각각이라면 특정 클럭에서 특정 작업을 해야하는데 그것이 되지 않으면 더 오래 걸리는것 처럼요.

좀전에 자동차공장을 얘로들었었는데 만약 승용차 공장에서 갑자기 트럭1대를 컨베이어벨트에서 만든다고 가정하면 부품의 갯수도 다르고 만들어지는 과정의 수도 다르기때문에 공장의 컨베이어 벨트 시스템은 효율적이지 못할 것입니다. Pipeline도 이와 마찬가지 입니다.

RISC는 명령어 형태가 단순, 고정되어있어서 연산을 해야하는 대상이 항상 일정하게 유지되어 Pipeline의 적용시 엄청난 효과를 보게 되는것입니다. SISC는 명령어형식이 RISC보다는 복잡해서 Pipeline의 적용시 데이터의크기가달라질때마다 손해(?)를 보는것입니다.

ps : 사실 컴퓨터구조 및 다른 이론서에는 저런형식으로 나와있지 않습니다. 이해를 돕기위해 그림을 그리다보니^^;

어쩌면 더 혼란스러워지실지도;; 개념적으로 설명한것이기때문에 참고만 하세요.

실제로는 계산방법도 있고 뭐 그런데...여기에 모두 적기에는..무리가;; 책도 더 찾아봐야하고..ㅎㅎ;

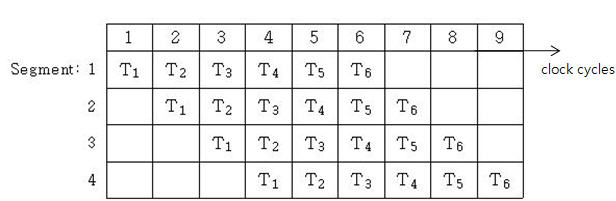

실제 "Computer System Architecture (3rd edition) - M. Morris Mano" 책에 나온 그림을 인용한

그림은 아래 따로 첨부한 그림을 참고하세요. 밑의 그림은 Space-time diagram for pipeline 라는 figure입니다.

[Study] PS/2 port (keyboard)

Double-J | 2008. 2. 12. 19:58

개발환경 : SPARTAN -3 Board

FPGA : Xilinx XC3S200

PS/2 port 를 보드에 인식시키는데 많은 자료가 없어서 약간 애를 먹었다.

일단 기본적인 동작은 PS/2 port를 사용하는 키보드는 다음과 같은 인터페이스이다.

위의 모양은 각 핀의 번호와 그 역할을 나타내 주고있다. 위의 자료는 Xilinx 의 SPARTAN-3 보드의 메뉴얼에서 참고한자료라

FPGA Pin 번호가 다음과 같다. 다른 보드를 사용할시 메뉴얼을 참고해야한다.

Device to Host 의 동작에서는 기본적으로 키보드가 정해진 클럭을 발생하고 그에따라 데이터비트도 변하게된다.

즉 위에서보면 PS/2 Pin의 1번, 5번을 통해 신호를 내보내고 이 신호를 받아 제어를 해야 한다.

CLK가 low일때 valid data 이다. 그러므로 state machine이 키보드에서 동작하는 크럭이 negative edge 일때 동작해야 한다

그럴때마다 데이터를 체크 하되 data bit는 다음과 같은 순서로 전달되는것을 주의 하도록 한다.

data는 총 11비트가 전송되게 되고 statr signal이 발생한이후로 차례로 8비트가 data bit이다.

이 data bit는 LSB부터 전송되게 되고 이 데이터는 키보드의 고유한 키값을 가지고 있다.

아래는 시뮬레이션의 결과이다.

※주의할점 :

임의의 키를 한번 눌렀다 떼면 누르는 순간 고유의 키값이 전달되고 떼는순간 F0가 전달되고 뒤이어 고유의 키값이 다시한번

전달된다.

참고한 사이트는 아래와 같다.

http://www.computer-engineering.org/index.php?title=PS/2_Mouse/Keyboard_Protocol

이 글은 스프링노트에서 작성되었습니다.

RSS 2.0

RSS 2.0 Tattertools

Tattertools Skin by ZF.

Skin by ZF.